# **SPI Library**

A software defined, industry-standard, SPI (serial peripheral interface) component that allows you to control an SPI bus via the xCORE GPIO hardware-response ports. SPI is a four-wire hardware bi-directional serial interface.

The SPI bus can be used by multiple tasks within the xCORE device and (each addressing the same or different slaves) and is compatible with other slave devices on the same bus.

## Features

- SPI master and SPI slave modes.

- Supports speed of up to 100 Mbit.

- Multiple slave device support

- All clock polarity and phase configurations supported.

## Typical Resource Usage

This following table shows typical resource usage in some different configurations. Exact resource usage will depend on the particular use of the library by the application.

| Configuration                           | Pins | Ports     | Clocks | Ram   | Logical cores |

|-----------------------------------------|------|-----------|--------|-------|---------------|

| Master (synchronous, zero clock blocks) | 4    | 4 (1-bit) | 0      | ~1.3K | 0             |

| Master (synchronous, one clock block)   | 4    | 4 (1-bit) | 1      | ~2.7K | 0             |

| Master (asynchronous)                   | 4    | 4 (1-bit) | 2      | ~3.3K | ≤ 1           |

| Slave (32 bit transfer mode)            | 4    | 4 (1-bit) | 1      | ~0.8K | ≤ 1           |

| Slave (8 bit transfer mode)             | 4    | 4 (1-bit) | 1      | ~0.8K | ≤ 1           |

The number of pins is reduced if either of the data lines are not required.

## Software version and dependencies

This document pertains to version 3.0.0 of this library. It is known to work on version 14.0.0 of the xTIMEcomposer tools suite, it may work on other versions.

The library does not have any dependencies (i.e. it does not rely on any other libraries).

## **Related application notes**

The following application notes use this library:

- AN00160 How to communicate as SPI master

- AN00161 How to communicate as SPI slave

# 1 External signal description

The SPI protocol requires a clock, one or more slave selects and either one or two data wires.

| SCLK | Clock line, driven by the master                           |

|------|------------------------------------------------------------|

| MOSI | Master Output, Slave Input data line, driven by the master |

| MISO | Master Output, Slave Input data line, driven by the slave  |

| SS   | Slave select line, driven by the master                    |

Table 1: SPI data wires

During any transfer of data, the master will assert the *SS* line and then output a series of transitions on the *SCLK* wire. During this time, the slave will drive data to be sampled by the master and the master will drive data to be sampled by the slave. At the end of the transfer, the *SS* is de-asserted.

If the slave select line is not driven high then the slave should ignore any transitions on the other lines.

#### 1.1 SPI modes

The data sample points for SPI are defined by the clock ploarity (CPOL) and clock phase (CPHA) parameters. SPI clock polarity may be inverted or non-inverted by the CPOL and the CPHA parameter is used to shift the sampling phase. The following for sections illustrate the MISO and MOSI data lines relative to the clock. The timings are given by:

| t1             | The minimum time from the start of the transaction to data being valid on the data pins.                |

|----------------|---------------------------------------------------------------------------------------------------------|

| t2             | The inter-transmission gap. This is the minimum amount of time that the slave select must be desserted. |

| MAX CLOCK RATE | This is the maximum clock rate supported by the configuration.                                          |

#### Table 2: SPI timings

The setup and hold timings are inherited from the underlying xCORE device. For details on these timing please refer to the device datasheet.

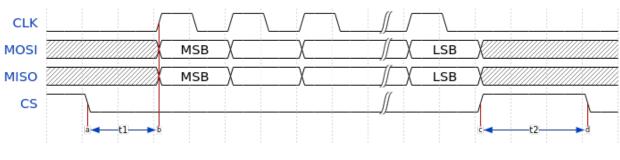

#### 1.1.1 Mode 0 - CPOL: 0 CPHA 1

The master and slave will drive out their first data bit on the first rising edge of the clock and sample on the subsequent falling edge.

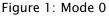

#### 1.1.2 Mode 1 - CPOL: 0 CPHA 0

The master and slave will drive out their first data bit before the first rising edge of the clock then drive on subsequent falling edges. They will sample on rising edges.

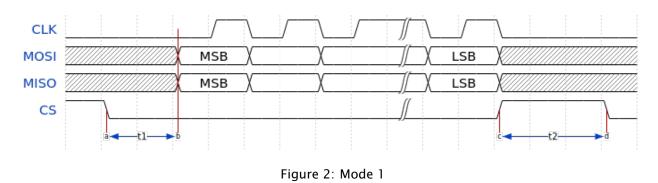

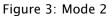

#### 1.1.3 Mode 2 - CPOL: 1 CPHA 0

The master and slave will drive out their first data bit before the first falling edge of the clock then drive on subsequent rising edges. They will sample on falling edges.

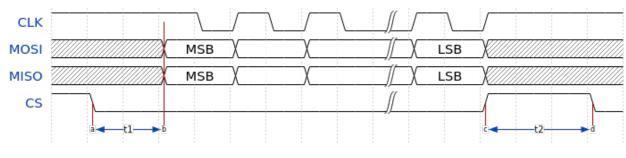

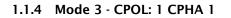

Figure 4: Mode 3

The master and slave will drive out their first data bit on the first falling edge of the clock and sample on the subsequent rising edge.

#### 1.2 SPI master timing characteristics

The application calls functions to begin a transaction (which asserts the slave select line) and to transfer data. So the minimum time between these (t1) can be controlled by the application.

The inter-transmission gap (t2) is also controlled by the user application since the function to specify the end of the transaction (i.e. the de-assertion of the slave select line) has an argument which is the mininum amount of time before which another transaction can start.

#### 1.2.1 Synchronous SPI master clock speeds

The maximum speed that the SPI bus can be driven depends on whether a clock block is used, the speed of the logical core that the SPI code is running on and where both the *MISO* and *MOSI* lines are used. The timings can be seen in Table 3.

| Clock blocks | MISO enabled | MOSI enabled | Max kbps (62.5<br>MHz core) | Max kbps (125<br>MHz core) |

|--------------|--------------|--------------|-----------------------------|----------------------------|

| 0            | 1            | 0            | 2497                        | 3366                       |

| 0            | 1            | 1            | 1765                        | 3366                       |

| 1            | 1            | 0            | 2149                        | 2149                       |

| 1            | 1            | 1            | 2149                        | 2149                       |

Table 3: SPI master timings (synchronous)

#### 1.2.2 Asynchronous SPI master clock speeds

The asynchronous SPI master is limited only by the clock divider on the clock block. This means that for the 100MHz reference clock, the asynchronous master can output a clock at up to 100MHz

| Clock blocks | MISO enabled | MOSI enabled | Max kbps (62.5<br>MHz core) | Max kbps (125<br>MHz core) |

|--------------|--------------|--------------|-----------------------------|----------------------------|

| 1            | x            | х            | 100000                      | 100000                     |

Table 4: SPI master timings (asynchronous)

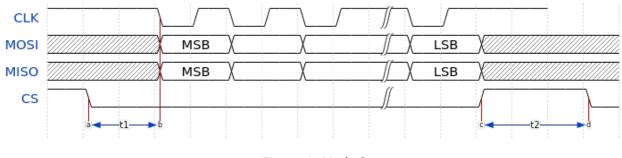

## 1.3 Connecting to the xCORE SPI master

The SPI wires need to be connected to the xCORE device as shown in Figure 5. The signals can be connected to any one bit ports on the device provide they do not overlap any other used ports and are all on the same tile.

Figure 5: SPI master connection to the xCORE device

If only one data direction is required then the *MOSI* or *MISO* line need not be connected. However, asynchronous mode is only supported if the MISO line is connected.

The master component of this library supports multiple slaves on unique slave select wires. This means that a single slave select assertion cannot be used to communicate with multiple slaves at the same time.

#### 1.4 SPI slave timings

The logical core running the SPI slave task will wait for the slave select line to assert and then begin processing the transaction. At this point is will call the master\_requires\_data callback to application code. The time taken for the application to perform this call will affect how long the logical core has to resume processing SPI data. This will affect the minimum allowable time between slave select changing and data transfer from the master (*t1*). The user of the library will need to determine this time based on their application.

After slave select is de-asserted the SPI slave task will call the master\_ends\_transaction callback. The time the application takes to process this will affect the minimum allowable inter-transmission gap between transactions (*t2*). The user of the library will also need to determine this time based on their application.

If the SPI slave task is combined will other tasks running on the same logical core then the other task may process an event delaying the time it takes for the SPI slave task to react to events. This will add these delays to the minimum times for both t1 and t2. The library user will need to take these into account in determining the timing restrictions on the master.

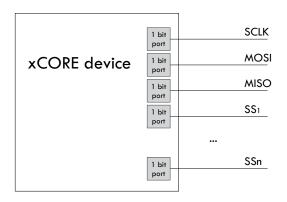

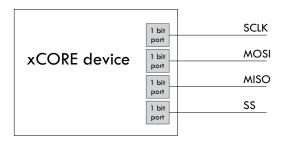

## 1.5 Connecting to the xCORE SPI slave

The SPI wires need to be connected to the xCORE device as shown in Figure 6. The signals can be connected to any one bit ports on the device provide they do not overlap any other used ports and are all on the same tile.

Figure 6: SPI slave connection to the xCORE device

The slave will only send and receive data when the slave select is driven high.

If the *MISO* line is not required then is need not be connected. The *MOSI* line must always be connected.

# 2 Usage

## 2.1 SPI master synchronous operation

There are two types of interface for SPI master components: synchronous and asynchronous.

The synchronous API provides blocking operation. Whenever a client makes a read or write call the operation will complete before the client can move on - this will occupy the core that the client code is running on until the end of the operation. This method is easy to use, has low resource use and is very suitable for applications such as setup and configuration of attached peripherals.

SPI master components are instantiated as parallel tasks that run in a par statement. For synchronous operation, the application can connect via an interface connection using the spi\_master\_if interface type:

Figure 7: SPI master task diagram

For example, the following code instantiates an SPI master component and connect to it:

```

= XS1_PORT_1A;

port p_miso

= {XS1_PORT_1B};

port p_ss[1]

port p_sclk

= XS1_PORT_1C;

port p_mosi

= XS1_PORT_1D;

clock clk_spi = XS1_CLKBLK_1;

int main(void) {

spi_master_if i_spi[1];

par {

spi_master(i_spi, 1, p_sclk, p_mosi, p_miso , p_ss, 1, clk_spi);

my_application(i_spi[0]);

}

return 0;

}

```

Note that the connection is an array of interfaces, so several tasks can connect to the same component instance. The slave select ports are also an array since the same SPI data lines can connect to several devices via different slave lines.

The final parameter of the spi\_master task is an optional clock block. If the clock block is supplied then the maximum transfer rate of the SPI bus is increased (see Table 3). If null is supplied instead then the performance is less but no clock block is used.

The application can use the client end of the interface connection to perform SPI bus operations e.g.:

```

void my_application(client spi_master_if spi) {

uint8_t val;

printf("Doing one byte transfer. Sending 0x22.\n");

spi.begin_transaction(0, 100, SPI_MODE_0);

val = spi.transfer8(0x22);

spi.end_transaction(1000);

printf("Read data %d from the bus.\n", val);

}

```

Here, begin\_transaction selects the device 0 and asserts its slave select line. The application can then transfer data to and from the slave device and finish with end\_transaction, which de-asserts the slave select line.

Operations such as spi.transfer8 will block until the operation is completed on the bus. More information on interfaces and tasks can be be found in the XMOS Programming Guide (see XM-004440-PC). By default the SPI synchronous master mode component does not use any logical cores of its own. It is a *distributed* task which means it will perform its function on the logical core of the application task connected to it (provided the application task is on the same tile).

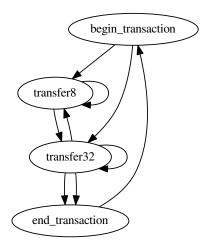

#### 2.1.1 Synchronous master usage state machine

The function calls made on the SPI master interface must follow the sequence shown by the state machine in Figure 8. If this sequence is not followed then the behavior is undefined.

Figure 8: SPI master use state machine

#### 2.2 SPI master asynchronous operation

The synchronous API will block your application until the bus operation is complete. In cases where the application cannot afford to wait for this long the asynchronous API can be used.

The asynchronous API offloads operations to another task. Calls are provide to initiate reads and writes and notifications are provided when the operation completes. This API requires more management in the application but can provide much more efficient operation. It is particularly suitable for applications where the SPI bus is being used for continuous data transfer.

Setting up an asynchronous SPI master component is done in the same manner as the synchronous component:

```

port p_miso

= XS1_PORT_1A;

port p_ss[1] = {XS1_PORT_1B};

port p_sclk

= XS1_PORT_1C;

= XS1_PORT_1D;

port p_mosi

clock cb0

= XS1_CLKBLK_1;

clock cb1

= XS1_CLKBLK_2;

int main(void) {

i2c_master_async_if i_spi[1];

par {

spi_master_async(i_spi, 1, p_sclk, p_mosi, p_miso, p_ss, 1, cb0, cb1);

my_application(i_spi[0]);

}

return 0;

}

```

The application can use the asynchronous API to offload bus operations to the component. This is done by moving pointers to the SPI slave task to transfer and then retrieving pointers when the operation is complete. For example, the following code repeatedly calculates 100 bytes to send over the bus and handles 100 bytes coming back from the slave:

```

void my_application(client spi_master_async_if spi) {

uint8_t outdata[100];

uint8_t indata[100];

uint8_t * movable buf_in = indata;

uint8_t * movable buf_out = outdata;

// create and send initial data

fill_buffer_with_data(outdata);

spi.begin_transaction(0, 100, SPI_MODE_0);

spi.init_transfer_array_8(move(buf_in), move(buf_out), 100);

while (1) {

select {

case spi.operation_complete():

retreive_transfer_buffers_8(buf_in, buf_out);

spi.end_transaction();

// Handle the data that has come in

handle_incoming_data(buf_in);

// Calculate the next set of data to go

fill_buffer_with_data(buf_out);

spi.begin_transaction(0, 100, SPI_MODE_0);

spi.init_transfer_array_8(move(buf_in), move(buf_out));

break;

}

}

}

```

The SPI asynchronous task is combinable so can be run on a logical core with other tasks (including the application task it is connected to).

#### 2.2.1 Asynchronous master command buffering

In order to provide asynchronous behaviour for multiple clients the asynchronous master will store up to one begin\_transaction and one init\_transfer\_array\_8 or init\_transfer\_array\_32 from each client. This means that if the master is busy doing a transfer for client X, then client Y will still be able to begin a transaction and send data fully asynchronously. Consequently, after client Y has issued init\_transfer\_array\_8 or init\_transfer\_array\_32 the it will be able to continue operation whilst waiting for the notification.

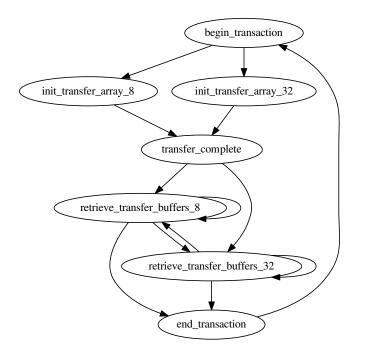

#### 2.2.2 Asynchronous master usage state machine

The function calls made on the SPI master asynchronous interface must follow the sequence shown by the state machine in Figure 9. If this sequence is not followed then the behavior is undefined.

Figure 9: SPI master use state machine (asynchronous)

#### 2.3 Master inter-transaction gap

For both synchronous and asynchronous modes the end\_transaction requires a slave select deassert time. This parameter will provide a minimum deassert time between two transaction on the same slave select. In the case where a begin\_transaction asserting the slave select would violate the previous end\_transaction then the begin\_transaction will block until the slave select deassert time has been satisified.

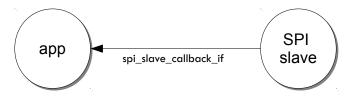

## 2.4 Slave usage

SPI slave components are instantiated as parallel tasks that run in a par statement. The application can connect via an interface connection.

Figure 10: SPI slave task diagram

For example, the following code instantiates an SPI slave component and connect to it:

```

out buffered port:32

miso = XS1_PORT_1A;

in port

p_ss = XS1_PORT_1B;

sclk = XS1_PORT_1C;

in port

in buffered port:32

mosi = XS1_PORT_1D;

clock

cb

= XS1_CLKBLK_1;

int main(void) {

interface spi_slave_callback_if spi_i;

par {

spi_slave(i, p_sclk, p_mosi, p_miso, p_ss, cb, SPI_MODE_0,

SPI_TRANSFER_SIZE_8);

my_application(i2c);

}

return 0;

}

```

When a slave component is instantiated the mode and transfer size needs to be specified.

The slave component acts as the client of the interface connection. This means it can "callback" to the application to respond to requests from the bus master. For example, the following code snippet shows part of an application that responds to SPI transactions where the first word is a command to read or write command and subsequent transfers either provide or consume data:

```

while (1) {

uint32_t command = 0;

size_t index = 0;

select {

case spi.master_requires_data() -> uint32_t data:

if (command == 0) {

// Not got the command yet. This will be the

// first word of the transaction.

data = 0;

} else if (command == READ_COMMAND) {

data = get_read_data_item(index);

index++;

} else {

data = 0;

}

break;

case spi.master_supplied_data(uint32_t data, uint32_t valid_bits):

if (command == 0) {

command = data;

} else if (command == WRITE_COMMAND) {

handle_write_data_item(data, index);

index++;

}

break;

case spi.master_ends_transaction():

// The master has de-asserted slave select.

command = 0;

index = 0;

break;

}

}

```

Note that the time taken to handle the callbacks will determine the timing requirements of the SPI slave. See application note AN00161 for more details on different ways of working with the SPI slave component.

## 2.5 Disabling data lines

The *MOSI* and *MISO* parameters of the spi\_master task are optional. So in the top-level par statement the function can be called with null instead of a port e.g.:

spi\_master(i\_spi, 1, p\_sclk, null, p\_miso , p\_ss, 1, clk\_spi);

Similarly, the *MOSI* parameter of the spi\_master\_async task is optional (but the *MISO* port must be provided).

The spi\_slave task has an optional MISO parameter (but the MOSI port must be supplied).

# 3 Master API

All SPI master functions can be accessed via the spi.h header:

```

#include <spi.h>

```

You will also have to add lib\_spi to the USED\_MODULES field of your application Makefile.

## 3.1 Supporting types

The following type is used to configure the SPI components.

| Туре        | spi_mode_t                                                 |

|-------------|------------------------------------------------------------|

| Description | This type indicates what mode an SPI component should use. |

| Values      | SPI_MODE_0<br>SPI Mode 0 - Polarity = 0, Clock Edge = 1.   |

|             | SPI_MODE_1<br>SPI Mode 1 - Polarity = 0, Clock Edge = 0.   |

|             | SPI_MODE_2<br>SPI Mode 2 - Polarity = 1, Clock Edge = 0.   |

|             | SPI_MODE_3<br>SPI Mode 3 - Polarity = 1, Clock Edge = 1.   |

# 3.2 Creating an SPI master instance

| Function    | spi_master                                                           |                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description | slaves on the<br>Each slave m<br>You can acc<br>vice_index p         | plements the SPI proctocol in master mode that is connected to a multiple<br>e bus.<br>Just be connected to using the same SPI mode.<br>ess different slave devices over the interface connection using the de-<br>parameter of the interface functions. The task will allocate the device<br>e order of the supplied array of slave select ports.                                        |

| Туре        | static<br>out buf<br>out buf<br>in buff<br>out por                   | <pre>(server interface spi_master_if i[num_clients],<br/>const size_t num_clients,<br/>fered port:32 sclk,<br/>fered port:32 ?mosi,<br/>ered port:32 ?miso,<br/>t p_ss[num_slaves],<br/>const size_t num_slaves,</pre>                                                                                                                                                                    |

| Parameters  | i<br>num_client<br>clk<br>sclk<br>mosi<br>miso<br>p_ss<br>num_slaves | an array of interface connection to the clients of the task.<br>s<br>the number of clients connected to the task.<br>a clock block used by the task.<br>the SPI clock port.<br>the SPI MOSI (master out, slave in) port.<br>the SPI MISO (master in, slave out) port.<br>an array of ports connected to the slave select signals of the slave.<br>The number of slave devices on the bus. |

|             | clk                                                                  | a clock for the component to use.                                                                                                                                                                                                                                                                                                                                                         |

| Function    | spi_master                                                                                                                                                                                                                                                                                                                                              | _async                                                                                                                    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Description |                                                                                                                                                                                                                                                                                                                                                         | component for asynchronous API.<br>nent implements SPI and allows a client to connect using the asynchronous<br>nterface. |

| Туре        | <pre>[[combinable]]<br/>void<br/>spi_master_async(<br/>server interface spi_master_async_if i[num_clients],<br/>static const size_t num_clients,<br/>out buffered port:32 sclk,<br/>out buffered port:32 ?mosi,<br/>in buffered port:32 ?mosi,<br/>out port p_ss[num_slaves],<br/>static const size_t num_slaves,<br/>clock clk0,<br/>clock clk1)</pre> |                                                                                                                           |

| Parameters  | i                                                                                                                                                                                                                                                                                                                                                       | an array of interface connection to the clients of the task.                                                              |

|             | num_client                                                                                                                                                                                                                                                                                                                                              | the number of clients connected to the task.                                                                              |

|             | sclk                                                                                                                                                                                                                                                                                                                                                    | the SPI clock port.                                                                                                       |

|             | mosi                                                                                                                                                                                                                                                                                                                                                    | the SPI MOSI (master out, slave in) port.                                                                                 |

|             | miso                                                                                                                                                                                                                                                                                                                                                    | the SPI MISO (master in, slave out) port.                                                                                 |

|             | p_ss                                                                                                                                                                                                                                                                                                                                                    | an array of ports connected to the slave select signals of the slave.                                                     |

|             | num_slaves                                                                                                                                                                                                                                                                                                                                              | The number of slave devices on the bus.                                                                                   |

|             | c1k0                                                                                                                                                                                                                                                                                                                                                    | a clock for the component to use.                                                                                         |

|             | clk1                                                                                                                                                                                                                                                                                                                                                    | a clock for the component to use.                                                                                         |

|             |                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                           |

# 3.3 SPI master interface

| Туре                     | spi_master_if                                                   |                                                                                                                                                                                                                                                                         |  |

|--------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Description              | This interface allows clients to interact with SPI master task. |                                                                                                                                                                                                                                                                         |  |

| Functions                |                                                                 |                                                                                                                                                                                                                                                                         |  |

|                          | Function                                                        | begin_transaction                                                                                                                                                                                                                                                       |  |

|                          | Description                                                     | Begin a transaction.<br>This will start a transaction on the bus. During a transaction,<br>no other client to the SPI component can send or receive data.<br>If another client is currently using the component then this call<br>will block until the bus is released. |  |

|                          | Туре                                                            | <pre>[[guarded]] void begin_transaction(unsigned device_index,</pre>                                                                                                                                                                                                    |  |

|                          | Parameters                                                      | device_index<br>the index of the slave device to interact with.<br>speed_in_khz                                                                                                                                                                                         |  |

|                          |                                                                 | The speed that the SPI bus should run at during the transaction (in kHZ).                                                                                                                                                                                               |  |

|                          |                                                                 | mode The mode of spi transfers during this transaction.                                                                                                                                                                                                                 |  |

| Function end_transaction |                                                                 | end_transaction                                                                                                                                                                                                                                                         |  |

|                          | Description                                                     | End a transaction.<br>This ends a transaction on the bus and releases the component<br>to other clients.                                                                                                                                                                |  |

|                          | Туре                                                            | <pre>void end_transaction(unsigned ss_deassert_time)</pre>                                                                                                                                                                                                              |  |

Continued on next page

| уре | spi_master_if (c |                                                                                                                                                                                    |

|-----|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Function         | transfer8                                                                                                                                                                          |

|     | Description      | Transfer a byte over the spi bus.<br>This function will transmit and receive 8 bits of data over the<br>SPI bus. The data will be transmitted least-significant bit first.         |

|     | Туре             | uint8_t transfer8(uint8_t data)                                                                                                                                                    |

|     | Parameters       | data the data to transmit the MOSI port.                                                                                                                                           |

|     | Returns          | the data read in from the MISO port.                                                                                                                                               |

|     | Function         | transfer32                                                                                                                                                                         |

|     | Function         |                                                                                                                                                                                    |

|     | Description      | Transfer a 32-bit word over the spi bus.<br>This function will transmit and receive 32 bits of data over the<br>SPI bus. The data will be transmitted least-significant bit first. |

|     |                  | This function will transmit and receive 32 bits of data over the                                                                                                                   |

|     | Description      | This function will transmit and receive 32 bits of data over the SPI bus. The data will be transmitted least-significant bit first.                                                |

# 3.4 SPI master asynchronous interface

| Туре        | spi_master_async_if                                                                                                                                                                              |                                                                                                                                                                                                                                                                         |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Description | Asynchronous interface to an SPI component.<br>This interface allows programs to offload SPI bus transfers to another task. An as<br>chronous notification occurs when the transfer is complete. |                                                                                                                                                                                                                                                                         |  |

| Functions   | Function                                                                                                                                                                                         | begin_transaction                                                                                                                                                                                                                                                       |  |

|             | Description                                                                                                                                                                                      | Begin a transaction.<br>This will start a transaction on the bus. During a transaction,<br>no other client to the SPI component can send or receive data.<br>If another client is currently using the component then this call<br>will block until the bus is released. |  |

|             | Туре                                                                                                                                                                                             | <pre>void<br/>begin_transaction(unsigned device_index,</pre>                                                                                                                                                                                                            |  |

|             | Parameters                                                                                                                                                                                       | device_index<br>the index of the slave device to interact with.<br>speed_in_khz<br>The speed that the SPI bus should run at during<br>the transaction (in kHZ)                                                                                                          |  |

|             |                                                                                                                                                                                                  | mode The mode of spi transfers during this transaction                                                                                                                                                                                                                  |  |

|             | Function<br>Description                                                                                                                                                                          | end_transactionEnd a transaction.This ends a transaction on the bus and releases the component                                                                                                                                                                          |  |

|             |                                                                                                                                                                                                  | to other clients.                                                                                                                                                                                                                                                       |  |

|             | Туре                                                                                                                                                                                             | <pre>void end_transaction(unsigned ss_deassert_time)</pre>                                                                                                                                                                                                              |  |

|             | Parameters                                                                                                                                                                                       | ss_deassert_time<br>The minimum time in reference clock ticks be-<br>tween assertions of the selected slave select. This<br>time will be ignored if the next transaction is to a<br>different slave select.                                                             |  |

Continued on next page

| Function    | init_transfer_array_8                                                                                                                                                                                                                    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description | Initialize Transfer an array of bytes over the spi bus.<br>This function will initialize a transmit of 8 bit data over the SPI<br>bus.                                                                                                   |

| Туре        | void<br>init_transfer_array_8(uint8_t *movable inbuf,<br>uint8_t *movable outbuf,<br>size_t nbytes)                                                                                                                                      |

| Parameters  | inbuf A <i>movable</i> pointer that is moved to the other task pointing to the buffer area to fill with data. If this parameter is NULL then the incoming data of the transfer will be discarded.                                        |

|             | outbuf A <i>movable</i> pointer that is moved to the other task<br>pointing to the buffer area to with data to trans-<br>mit. If this parameter is NULL then the outgoing<br>data of the transfer will consist of undefined val-<br>ues. |

|             | nbytes The number of bytes to transfer over the bus.                                                                                                                                                                                     |

| Function    | init_transfer_array_32                                                                                                                                                                                                                   |

| Descriptio  | Initialize Transfer an array of bytes over the spi bus.<br>This function will initialize a transmit of 32 bit data over the SPI<br>bus.                                                                                                  |

| Туре        | void<br>init_transfer_array_32(uint32_t *movable inbuf,<br>uint32_t *movable outbuf,<br>size_t nwords)                                                                                                                                   |

| Parameters  | inbuf A <i>movable</i> pointer that is moved to the other task pointing to the buffer area to fill with data. If this parameter is NULL then the incoming data of the transfer will be discarded.                                        |

|             | outbuf A <i>movable</i> pointer that is moved to the other task<br>pointing to the buffer area to with data to trans-<br>mit. If this parameter is NULL then the outgoing<br>data of the transfer will consist of undefined val-<br>ues. |

|             | nwords The number of words to transfer over the bus.                                                                                                                                                                                     |

Continued on next page

| Туре | spi_master_async_if (continued) |                                                                                                                                                                                                |  |  |

|------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|      | Function                        | transfer_complete                                                                                                                                                                              |  |  |

|      | Description                     | Transfer completed notification.<br>This notification occurs when a transfer is completed.                                                                                                     |  |  |

|      | Туре                            | <pre>[[notification]] slave void transfer_complete(void)</pre>                                                                                                                                 |  |  |

|      | Function                        | retrieve_transfer_buffers_8                                                                                                                                                                    |  |  |

|      | Description                     | Retrieve transfer buffers.<br>This function should be called after the transfer_complete()<br>notification and will return the buffers given to the other task<br>by init_transfer_array_8().  |  |  |

|      | Туре                            | <pre>[[clears_notification]] void retrieve_transfer_buffers_8(uint8_t *movable &amp;inbuf,     uint8_t *movable &amp;outbuf)</pre>                                                             |  |  |

|      | Parameters                      | inbuf A movable pointer that will be set to the buffer pointer that was filled during the transfer.                                                                                            |  |  |

|      |                                 | outbuf A movable pointer that will be set to the buffer<br>pointer that was transmitted during the transfer.                                                                                   |  |  |

|      | Function                        | retrieve_transfer_buffers_32                                                                                                                                                                   |  |  |

|      | Description                     | Retrieve transfer buffers.<br>This function should be called after the transfer_complete()<br>notification and will return the buffers given to the other task<br>by init_transfer_array_32(). |  |  |

|      | Туре                            | <pre>[[clears_notification]] void retrieve_transfer_buffers_32(uint32_t *movable &amp;inbu uint32_t *movable &amp;outbuf)</pre>                                                                |  |  |

|      | Parameters                      | inbuf A movable pointer that will be set to the buffer pointer that was filled during the transfer.                                                                                            |  |  |

|      |                                 | outbuf A movable pointer that will be set to the buffer pointer that was transmitted during the transfer.                                                                                      |  |  |

# 4 Slave API

All SPI slave functions can be accessed via the spi.h header:

#include <spi.h>

You will also have to add lib\_spi to the USED\_MODULES field of your application Makefile.

## 4.1 Creating an SPI slave instance

| Function    | spi_slave                                                                                                                                                                                                                                                                                         |                                                                                                                                     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Description | SPI slave component.<br>This function implements an SPI slave bus.                                                                                                                                                                                                                                |                                                                                                                                     |

| Туре        | <pre>[[combinable]]<br/>void<br/>spi_slave(client spi_slave_callback_if spi_i,<br/>in port p_sclk,<br/>in buffered port:32 p_mosi,<br/>out buffered port:32 ?p_miso,<br/>in port p_ss,<br/>clock clk,<br/>static const spi_mode_t mode,<br/>static const spi_transfer_type_t transfer_type)</pre> |                                                                                                                                     |

| Parameters  | spi_i                                                                                                                                                                                                                                                                                             | The interface to connect to the user of the component. The component acts as the client and will make callbacks to the application. |

|             | p_sclk                                                                                                                                                                                                                                                                                            | the SPI clock port.                                                                                                                 |

|             | p_mosi                                                                                                                                                                                                                                                                                            | the SPI MOSI (master out, slave in) port.                                                                                           |

|             | p_miso                                                                                                                                                                                                                                                                                            | the SPI MISO (master in, slave out) port.                                                                                           |

|             | p_ss                                                                                                                                                                                                                                                                                              | the SPI SS (slave select) port.                                                                                                     |

|             | clk                                                                                                                                                                                                                                                                                               | clock to be used by the component.                                                                                                  |

|             | mode                                                                                                                                                                                                                                                                                              | the SPI mode of the bus.                                                                                                            |

|             | transfer_                                                                                                                                                                                                                                                                                         | type<br>the type of transfer the slave will perform: either<br>SPI_TRANSFER_SIZE_8 or SPI_TRANSFER_SIZE_32.                         |

| Туре        | spi_transfer_type_tThis type specifies the transfer size from the SPI slave component to the application. |  |

|-------------|-----------------------------------------------------------------------------------------------------------|--|

| Description |                                                                                                           |  |

| Values      | SPI_TRANSFER_SIZE_8<br>Transfers should by 8-bit.                                                         |  |

|             | SPI_TRANSFER_SIZE_32<br>Transfers should be 32-bit.                                                       |  |

## 4.2 The SPI slave interface API

| Туре        | spi_slave_callback_if                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Description | This interface allows clients to interact with SPI slave tasks by completing callback that show how to handle data. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Functions   | Function                                                                                                            | master_ends_transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|             | Description                                                                                                         | This callback will get called when the master de-asserts on the slave select line to end a transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|             | Туре                                                                                                                | <pre>void master_ends_transaction(void)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|             | Function                                                                                                            | master_requires_data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|             | Description                                                                                                         | This callback will get called when the master initiates a bus<br>transfer or when more data is required during a transaction.<br>The application must supply the data to transmit to<br>the master. If the spi slave component is set to<br>SPI_TRANSFER_SIZE_32 mode then this callback will not be<br>called and master_requires_data32() will be called instead.<br>Data is transmitted for the least significant bit first. If the mas-<br>ter completes the transaction before 8 bits are transferred the<br>remaining bits are discarded. |  |

|             | Туре                                                                                                                | <pre>uint32_t master_requires_data(void)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|             | Returns                                                                                                             | the 8-bit value to transmit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|             | Function                                                                                                            | master_supplied_data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|             | Description                                                                                                         | This callback will get called after a transfer.<br>It will occur after every 8 bits transferred if the slave component<br>is set to SPI_TRANSFER_SIZE_8. If the component is set to<br>SPI_TRANSFER_SIZE_32 then it will occur if the master ends<br>the transaction before 32 bits are transferred.                                                                                                                                                                                                                                            |  |

|             | Туре                                                                                                                | <pre>void master_supplied_data(uint32_t datum,</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|             | Parameters                                                                                                          | datum the data received from the master.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|             |                                                                                                                     | the number of valid bits of data received from the master.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

## **APPENDIX A** - Known Issues

There are no known issues with this library.

# APPENDIX B - SPI library change log

## B.1 2.0.0

• Consolidated version, major rework from previous SPI components

XMOS®

Copyright © 2015, All Rights Reserved.

Xmos Ltd. is the owner or licensee of this design, code, or Information (collectively, the "Information") and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. Xmos Ltd. makes no representation that the Information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.